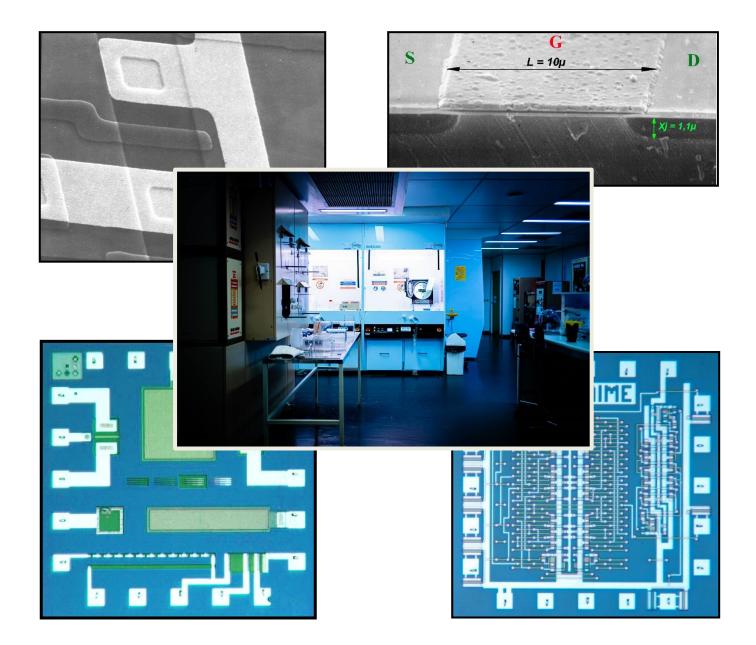

YTECHNIQUE DE TOULOUSE - INSTITUT NATIONAL DES SCIENCES APPLIQUEES DE TOULOUSE - LABORATOIRE D'ANALYSE ET D'ARCHITECTURE DES SYSTEMES - UNIVERSITE PA ATELIER INTERUNIVERSITAIRE DE MICRO-NANO-ÉLECTRONIQUE Pôle CNFM de TOULOUSE

# NMOS FABRICATION PROCESS

# Table of contents

| EVACUA | ATION INSTRUCTIONS FOR TEACHERS               | Erreur ! Signet non défini. |

|--------|-----------------------------------------------|-----------------------------|

| SECURI | TY INSTRUCTIONS                               | Erreur ! Signet non défini. |

| HANDLI | NG INSTRUCTIONS                               | 5                           |

| CLEANR | OOM ENTRY PROCEDURE                           | Erreur ! Signet non défini. |

| PROCES | S SHEET : TRANSISTOR WITH POLYSILICON GATE    | Erreur ! Signet non défini. |

| I-     | SUBSTRATE CHARACTERIZATION                    | 7                           |

| 11-    | MASKING OXIDE                                 | 7                           |

| 111-   | PHOTOLITHOGRAPHY n° 1 : "OPENING TRANSISTORS" |                             |

| IV-    | ORGANIC DECONTAMINATION                       | 9                           |

| V-     | R.C.A. CLEANING                               | 9                           |

| VI-    | GATE OXIDATION                                |                             |

| VII-   | POLYSILICON DEPOSIT                           |                             |

| VIII-  | PHOTOLITHOGRAPHY n° 2: " POLYSILICON ETCHING" |                             |

| IX-    | ORGANIC DECONTAMINATION                       |                             |

| X-     | SOURCE AND DRAIN DIFFUSION (N type)           |                             |

| XI-    | SiO2 L.T.O (Low Temperature Oxide) DEPOSIT    |                             |

| XII-   | PHOTOLITHOGRAPHY n° 3 : " CONTACTS OPENING"   |                             |

| XIII-  | METALLIZATION                                 | 15                          |

| XIV-   | PHOTOLITHOGRAPHY n° 4 : " METAL ETCHING"      | 15                          |

| XV-    | METAL ANNEALING                               |                             |

| XVI-   | WAFER TESTING                                 |                             |

| XVII-  | ASSEMBLY                                      |                             |

| XVIII- | ELECTRICAL CHARACTERIZATION                   |                             |

| XIX-   | OPERATIONS ON TEST-WAFERS                     |                             |

| XX-    | CHARACTERIZATIONS                             | 21                          |

| XXI-   | MESURE DES PROFONDEURS DE JONCTIONS           | 23                          |

| XXII-  | 4 PROBES RESISTIVITY MEASUREMENTS             | 24                          |

| XXIII- | SIDE VIEW OF PROCESS STEPS                    |                             |

| XXIV-  | DTC4R MASKS LEVEL                             | 27                          |

| XXV-   | ELECTRICAL TESTS FORM                         |                             |

# EVACUATION INSTRUCTIONS FOR TEACHERS

**REMINDER :** Each teacher is responsible for the orderly and calm evacuation of all students under his care at the time of the incident.

#### IN THE MAIN CLEAN ROOM:

- $\Rightarrow$  Evacuate the students by the emergency exit which leads directly into the hall.

- $\Rightarrow$  Do not go through the airlock again; do not undress.

- $\Rightarrow$  Exit through the main entrance of AIME.

#### IN THE PHOTOLITHOGRAPHY ROOM:

- $\Rightarrow$  Evacuate the students by the emergency exit which leads directly into the corridor.

- $\Rightarrow$  Do not go through the airlock again; do not undress.

- $\Rightarrow$  Exit through the main entrance of AIME.

#### IN ASSEMBLY OR CHARACTERIZATION ROOMS:

- $\Rightarrow$  Evacuate the students through the emergency exit leading to the green space behind the AIME.

- $\Rightarrow$  Do not go through the airlock again; do not undress.

- $\Rightarrow$  Take a tour of AIME.

#### GATHER ALL STUDENTS AT THE GATHERING POINT IN FRONT OF AIME.

#### TAKE A CENSUS.

#### DO NOT REINSTATE THE PREMISES WITHOUT THE ADVICE OF THE PERSONNEL IN CHARGE OF EVACUATION

#### SECURITY INSTRUCTIONS

#### LOCATE THE SAFETY EQUIPMENT:

- emergency exits

- security showers

- fire extinguishers

- self-contained breathing equipment

#### WEAR PROTECTIVE GLASSES IS MANDATORY FOR:

- CHEMICAL CLEANING (RCA AND H<sub>2</sub>SO<sub>4</sub>-H<sub>2</sub>O<sub>2</sub>)

- ALL WET ATTACKS

# TRAINEES ARE **FORBIDDEN** TO TRANSPORT CHEMICALS FROM ONE WORKSTATION TO ANOTHER.

Keep in mind that:

- gloves are compulsory but they do not provide sufficient protection against high temperatures or corrosive products,

- some baths give off noxious vapors, normally drawn in by laminar flow hoods,

- overshoes sometimes make the floor very slippery.

# HANDLING INSTRUCTIONS

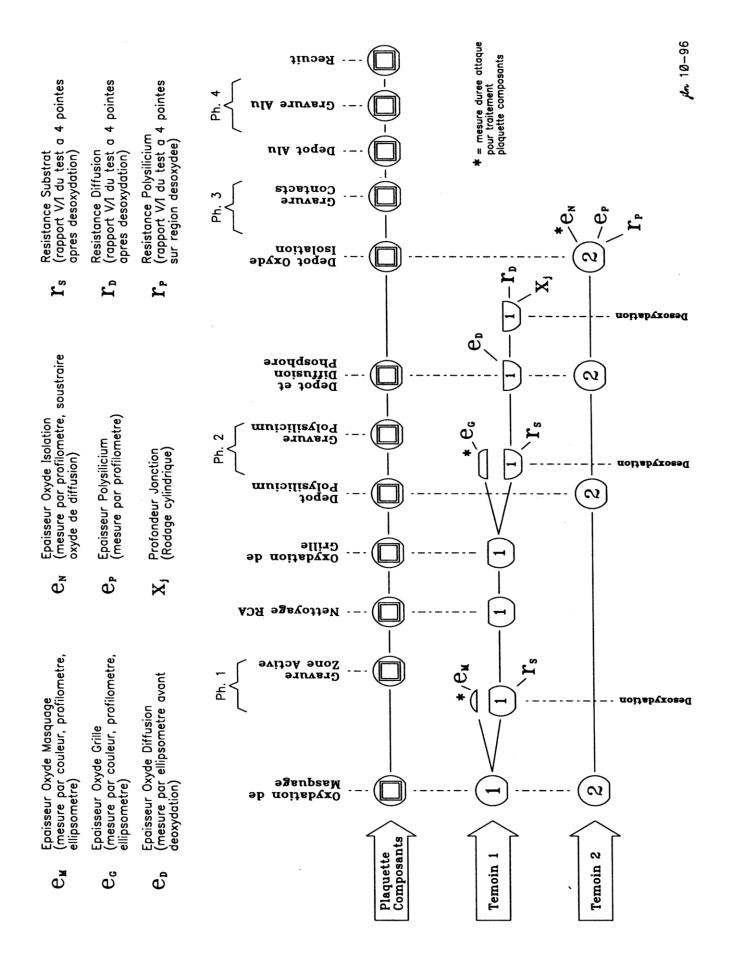

- Throughout the duration of the process, the quality control of each step must be a permanent concern if we want to achieve a final component in working order, as well as a good performance on the whole. For this purpose, we will use in parallel with the "components" wafer, a control/test wafer ("witness") which will characterize each step carried out.

- Warning: the wafers boxes must be opened by turning the cover clockwise

- For handling a wafer with a tweezer :

- take advantage of the flat if the wafer is in the box

- pinch at least 5mm from the edge of the wafer to reduce the risk of breakage. Any wafer coming out of a wet treatment must at the end undergo a rinsing with D.I. water and mechanical drying before being stored in its box.

- A good rinsing must include a change of tweezer, it is necessary to have a second one available and clean all tweezers.

- The tips of the pliers must not be wiped (neither on the gown, nor on paper), they must be rinsed with water and dried with nitrogen.

- The function of the gloves is to protect the components from contamination. Contamination of gloves should also be avoided. They are absolutely not an effective protection against acids.

- The plastic of the boxes cannot withstand temperatures above 250 ° C. In particular, cool down the wafers coming out from oven, for about 20 seconds in the open air.

- Paper is a source of contamination, make minimal use of it.

# **CLEANROOM ENTRY PROCEDURE**

- Leave street clothes and bags in the seminar room.

- Six lockers, lockable, can be used in the SAS for valuables.

- No more than 4 people in the airlock at the same time

#### Clean room entry:

| <u>Lab coat</u> : | white :<br>blue:<br>green:      | permanent staff<br>trainees<br>visitors                                       |

|-------------------|---------------------------------|-------------------------------------------------------------------------------|

| Overshoes:        | place the sear<br>Do not put yo | n inside.<br>our foot in the clean part until you have put on your overshoes. |

| Mob caps:         | Provision in t                  | he wall dispenser.                                                            |

| Gloves:           | Provision in t                  | he wall dispenser. 2 sizes available.                                         |

#### Exit of clean room:

<u>Lab coat/mob caps/goggles</u>: place them in your personal box <u>Overshoes/gloves</u>: throw them in dedicated trashes.

#### **Recommendations:**

- Be careful not to enter the airlock with muddy or wet dress shoes (use the doormat at the entrance of the AIME).

- Limit the number of objects and documents entering the Clean Room (carbon pencil prohibited).

# PROCESS SHEET: TRANSISTOR WITH POLYSILICON GATE

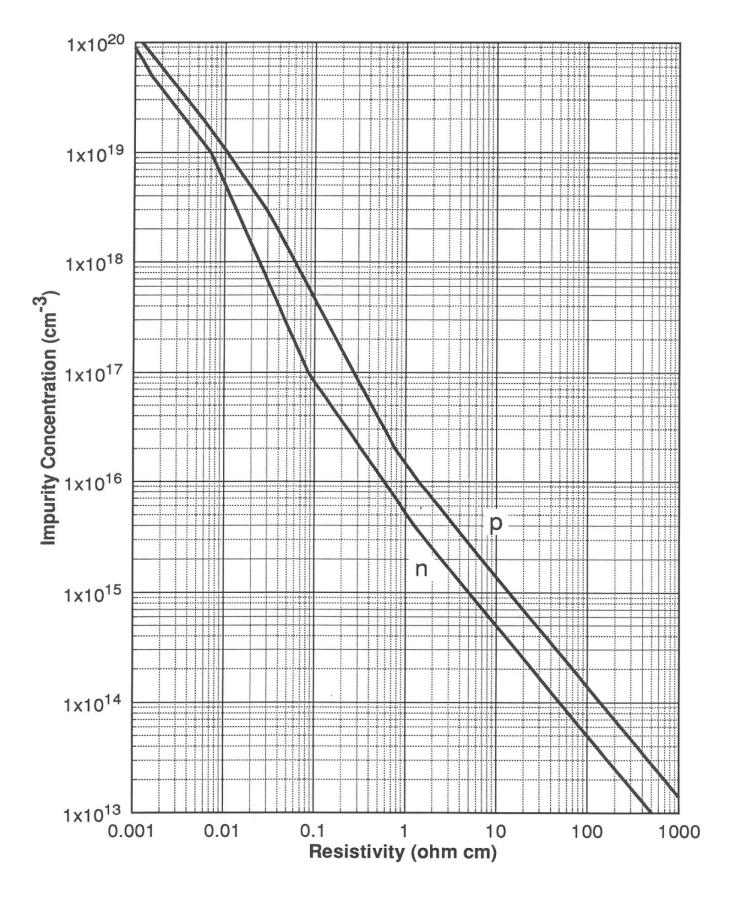

# I- SUBSTRATE CHARACTERIZATION

#### COMPONENTS WAFERS n° ... :

#### MATERIAL: Si P type, orientation : (100)

| $\bigcirc$ wafer thickness measurement      | $e_s =$          | μm                  |

|---------------------------------------------|------------------|---------------------|

| $\bigcirc$ 4 probes measurement             | V/I =            | Ω                   |

| $\bigcirc$ sheet resistance calculation     | R =              | $\Omega/_{\Box}$    |

| $\bigcirc$ resistivity calculation          | $\rho_s =$       | Ω.cm.               |

| $\bigcirc$ doping concentration calculation | N <sub>A</sub> = | at.cm <sup>-3</sup> |

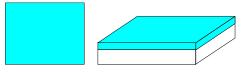

#### II- MASKING OXIDE

## **<u>1- Cleaning before Oxidation:</u>**

| Operations                                     | Conditions                      |

|------------------------------------------------|---------------------------------|

| $\subset 1^{\circ}$ ) Degreasing               | Acetone                         |

| $\bigcirc 2^{\circ}$ ) Rinsing                 | DI water                        |

| $\bigcirc$ 3°) Chemical Oxidation              | $H_2SO_4 + H_2O_2(1/1) - 2 min$ |

| $\bigcirc 4^{\circ}$ ) Rinsing                 | DI water                        |

| $\subset 5^{\circ}$ ) SiO <sub>2</sub> etching | BOE HF - 30 s                   |

| $\subset \supset 6^{\circ}$ ) Rinsing          | DI water                        |

| $\bigcirc$ 7°) Drying                          | Spin dryer                      |

| $\bigcirc 8^{\circ}$ ) Washing - Drying        | Washer dryer                    |

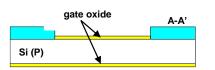

# **<u>2- Wet thermal Oxidation:</u>** This operation is performed inside oven N° 2-2

| masking oxide |  |

|---------------|--|

| Si (P)        |  |

| masking oxyde |  |

|                                            |          | Conditions                          |  |  |

|--------------------------------------------|----------|-------------------------------------|--|--|

| $\bigcirc$ process also test-wafer 1 and 2 |          |                                     |  |  |

| Temperature                                | Duration | Flow rates                          |  |  |

| $\bigcirc$ from 800°C to 1100°C            | 25 min   | $N_2 = 1 l/min$                     |  |  |

| ⊂⊃ 1100°C                                  | 35 min   | $H_2 = 2,3 l/min - O_2 = 1,5 l/min$ |  |  |

| ⊂⊃ 1100°C                                  | 30 min   | $O_2 = 2,2 $ l/min                  |  |  |

| ⊂⊃ 1100°C                                  | 5 min    | Ar = 1,5 l/min                      |  |  |

| $\Box$ from 1100°C to 800°C                | 60 min   | $N_2 = 1 l/min$                     |  |  |

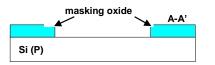

# III- PHOTOLITHOGRAPHY n° 1: "TRANSISTOR OPENING"

This step provides the channel width «  $\mathbf{W}$  » of the transistor.

| Supervisor's visa for the continuation of Operations |                                                     |  |

|------------------------------------------------------|-----------------------------------------------------|--|

| Operations Conditions                                |                                                     |  |

| $\bigcirc$ 1°) Drying                                | Hot plate 120°C – 2 min                             |  |

| ⊂⊃ 2°) HMDS Deposit<br>(Adhesion promoter)           | Spin coater 4000 rpm - 30 s                         |  |

| $\bigcirc$ 3°) Positive photoresist deposit          | Resist Shipley S1813<br>Spin coater 4000 rpm - 30 s |  |

| $\subset 4^{\circ}$ ) 1st annealing                  | Hot plate $100^{\circ}C - 60 s$                     |  |

| $\bigcirc$ 5°) Alignment - Insolation                | Mask $n^{\circ}1 - 5$ s                             |  |

| $\subset 5^{\circ}$ ) Development                    | Bath at 20 °C - 25 s                                |  |

| $\bigcirc 7^{\circ}$ ) Rinsing                       | DI water                                            |  |

| $\bigcirc 8^{\circ}$ ) Drying                        | Spin dryer                                          |  |

| $\bigcirc 9^{\circ}$ ) Observation                   | Optical microscope                                  |  |

| $\bigcirc$ 10°) 2nd annealing                        | Hot plate 120° C - 45 s                             |  |

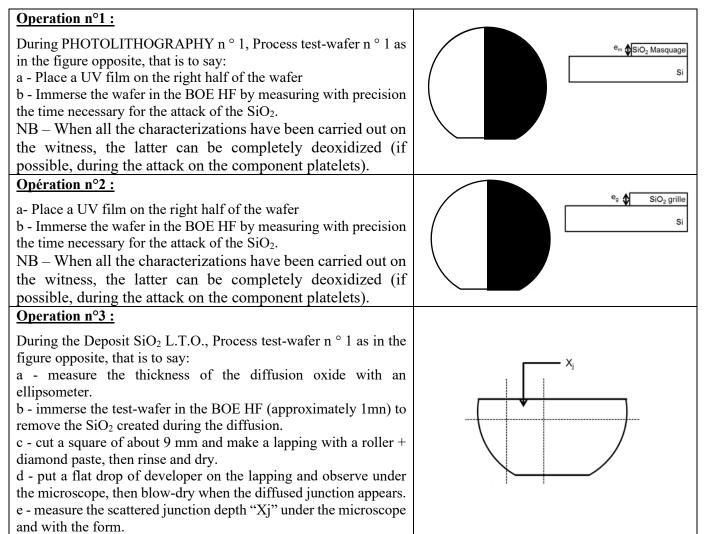

| ⊂⊃ Process test wafer 1                              | Operation n°1 (§ XIX)                               |  |

| $\subset 11^{\circ}$ ) SiO <sub>2</sub> etching      | BOE HF : time duration given by test-wafer1         |  |

| $\bigcirc$ 12°) Rinsing                              | DI water                                            |  |

| $\bigcirc$ 13°) Drying                               | Spin dryer                                          |  |

| $\bigcirc$ 14°) Observation                          | Optical microscope                                  |  |

| $\subset 15^{\circ}$ ) Resist dissolution            | Acetone                                             |  |

| $\bigcirc$ 16°) Rinsing       | DI water   |

|-------------------------------|------------|

| $\subset 17^{\circ}$ ) Drying | Spin dryer |

# IV- ORGANIC DECONTAMINATION

| Operations                     | Conditions                 |

|--------------------------------|----------------------------|

| $\subset 1^{\circ}$ ) Cleaning | $H_2SO_4 + H_2O_2 - 2 min$ |

| $\bigcirc 2^{\circ}$ ) Rinsing | DI water                   |

| $\bigcirc 3^{\circ}$ ) Drying  | Spin dryer                 |

## V- CLEANING R.C.A.

This operation aims to prepare the Si - SiO<sub>2</sub> interface before growing the gate oxide, following 5 steps (A' -A - A' - B - C):

| Conditions                                                                  |                                           |  |

|-----------------------------------------------------------------------------|-------------------------------------------|--|

| $\bigcirc$ clean at the same time test-wafer 1, <u>but not test-wafer 2</u> |                                           |  |

| Operations Conditions                                                       |                                           |  |

| $\subset 1^{\circ}$ ) Bath A'                                               | Dilute HF – 30 s                          |  |

| $\bigcirc 2^{\circ}$ ) Rinsing                                              | DI water – 3 min minimum                  |  |

| $\subset 3^{\circ}$ ) Drying                                                | Spin dryer                                |  |

| $\bigcirc 4^{\circ}$ ) Bath A                                               | HNO <sub>3</sub> boiling – 10 min         |  |

| $\subset 5^{\circ}$ ) Rinsing                                               | DI water – 3 min minimum                  |  |

| $\subset \supset 6^{\circ}$ ) Bath A'                                       | Dilute HF – 30 s                          |  |

| $\bigcirc$ 7°) Rinsing                                                      | DI water – 3 min minimum                  |  |

| $\subset > 8^{\circ}$ ) Bath B                                              | $NH_4OH + H_2O_2 + H_2O$ boiling - 10 min |  |

| $\bigcirc 9^{\circ}$ ) Rinsing                                              | DI water – 3 min minimum                  |  |

| $ ightarrow 10^{\circ}$ ) Bath C                                            | $HCl + H_2O_2 + H_2O$ boiling - 5 min     |  |

| $ ightarrow 11^{\circ}$ ) Rinsing                                           | DI water – 3 min minimum                  |  |

| $\bigcirc$ 12°) Drying                                                      | Spin dryer                                |  |

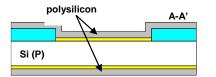

#### VI- GATE OXIDE

This dry Oxidation is performed in oven N° 2-1 following two steps:

| Conditions                                                |          |                 |  |  |

|-----------------------------------------------------------|----------|-----------------|--|--|

| ⊂⊃ Process test-wafer 1 also, <u>but not test-wafer 2</u> |          |                 |  |  |

| Temperature                                               | Duration | Flow rates      |  |  |

| ⊂⊃ 1100°C                                                 | 20 min   | $O_2 = 2 l/min$ |  |  |

| ⊂⊃ 1100°C                                                 | 10 min   | Ar = 2 l/min    |  |  |

During this operation, continue to characterize the process (cf part XX "characterizations")

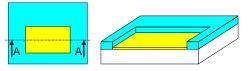

#### VII- POLYSILICON DEPOSIT

This is performed in the LPCVD (Low Pressure Chemical Vapor Deposition) reactor n°4-3:

| Conditions                           |                                                           |                                        |           |  |  |

|--------------------------------------|-----------------------------------------------------------|----------------------------------------|-----------|--|--|

| $\bigcirc$ Process also test-wafer 2 | ⊂⊃ Process also test-wafer 2, <u>but not test-wafer 1</u> |                                        |           |  |  |

| Temperature                          | Duration                                                  | Flow rates                             | Pressure  |  |  |

| $\bigcirc$ from 400°C to 585°C       | 20 min                                                    | $N_2 = 1 l/min$                        | 1 Torr    |  |  |

| ⊂⊃ 585°C                             | 21 min                                                    | $SiH_4 = 50 cc/min$                    | 250 mTorr |  |  |

| $\bigcirc$ from 585°C to 400°C       | 20 min                                                    | $N_2 = 1$ l/min (cycles de purge/vide) | 1 Torr    |  |  |

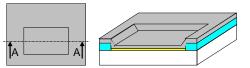

# VIII- PHOTOLITHOGRAPHY n° 2: "POLYSILICON ETCHING"

| S                                                    | upervisor's visa for the continuation of Operations                                                       |   |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---|

| Operations                                           | Conditions                                                                                                | • |

| $\Box 1^{\circ}$ ) Drying                            | Hot plate $120^{\circ}C - 2 \min$                                                                         |   |

| $\bigcirc$ 2°) HMDS deposit<br>(Adhesion promoter)   | Spin coater 4000 rpm - 30 s                                                                               |   |

| $\bigcirc$ 3°) Positive photoresist deposit          | Resist Shipley S1813<br>Spin coater 4000 rpm - 30 s                                                       |   |

| $\subset 4^{\circ}$ ) 1st annealing                  | Hot plate 100°C - 60 s.                                                                                   |   |

| $\bigcirc 5^{\circ}$ ) Alignment - Insolation        | Mask $n^{\circ}2 - 5$ s                                                                                   |   |

| $\subset 6^{\circ}$ ) Development                    | Bath at 20 °C - 25 s                                                                                      |   |

| $\bigcirc$ 7°) Rinsing                               | DI water                                                                                                  |   |

| $\bigcirc 8^{\circ}$ ) Drying                        | Spin dryer                                                                                                |   |

| $\bigcirc$ 9°) Observation                           | Optical microscope                                                                                        |   |

| $\bigcirc$ 10°) 2nd annealing                        | Hot plate 120° C - 45 s                                                                                   |   |

| ⊂⊃ 11°) POLYSILICON ETCHING<br>(components side)     | REACTIVE ION ETCHING<br>Flow rate SF <sub>6</sub> : 30 cc/min.<br>Pressure : 0,02 mbar<br>Power RF : 50 W |   |

| $\subset 12^{\circ}$ ) Do not remove the photoresist |                                                                                                           |   |

| $\subset 13^{\circ}$ ) Observation                   | Optical microscope                                                                                        |   |

| ⊂⊃ Process test-wafer 1                              | Operation n°2 (§ XIX)                                                                                     |   |

| ⊂⊃ 14°) SiO2 etching                                 | BOE HF: time duration given by test-wafer1                                                                |   |

| $\bigcirc$ 15°) Rinsing                              | DI water                                                                                                  |   |

| $\bigcirc$ 16°) Drying                               | Spin dryer                                                                                                |   |

| $\bigcirc$ 17°) Observation                          | Optical microscope                                                                                        |   |

| $\bigcirc$ 18°) Resist dissolution                   | Acetone + DI water                                                                                        |   |

Source and drain are opened for diffusion so the channel length "L" will be set under the gate.

# IX- ORGANIC DECONTAMINATION

| Operations                     | Conditions                 |

|--------------------------------|----------------------------|

| $\subset 1^{\circ}$ ) Cleaning | $H_2SO_4 + H_2O_2 - 2 min$ |

| $\bigcirc 2^{\circ}$ ) Rinsing | DI water                   |

| $\subset 3^{\circ}$ ) Drying   | Spin dryer                 |

# X- SOURCE ET DRAIN DIFFUSION (N type)

**<u>1- PreDeposit :</u>** This operation is performed following 3 steps in oven n°1-1

|                                           |          | Conditions                                             |

|-------------------------------------------|----------|--------------------------------------------------------|

| $\square$ Process also test-wafer 1 and 2 |          |                                                        |

| Temperature                               | Duration | Flow rates                                             |

| ⊂⊃ 1050°C                                 | 5 min    | $N_2 = 2 l/min - O_2 = 0,1 l/min$                      |

| ⊂⊃ 1050°C                                 | 10 min   | $N_2 = 2 l/min - O_2 = 0,1 l/min - POCl_3 = 10 mg/min$ |

| ⊂⊃ 1050°C                                 | 6 min    | $N_2 = 2 l/min - O_2 = 0,1 l/min$                      |

<u>**2- Drive-in :**</u> This operation is performed in oven  $n^{\circ}1-1$  following these conditions :

| Temperature | Duration | Flow rates      |

|-------------|----------|-----------------|

| ⊂⊃ 1100°C   | 7 min    | $N_2 = 1 l/min$ |

| Supervisor's visa for the continuation of Operations                                                                  | ▼ |

|-----------------------------------------------------------------------------------------------------------------------|---|

| $\subset \supset$ Diffusion oxyde e <sub>d</sub> thickness measurement on test-wafer 1 - <b>Operation n°3 (§ XIX)</b> |   |

| $\bigcirc$ 4 probes measurement (Oxide etching and V/I)                                                               |   |

# XI- SiO2 DEPOSIT L.T.O (Low Temperature Oxide)

After the source and drain diffusion, an insulating capping layer of SiO<sub>2</sub> L.T.O. (low temperature oxide) is deposited. This operation is performed in oven LPCVD n°3-1 following the conditions:

| Conditions                                                |          |                                                       |           |

|-----------------------------------------------------------|----------|-------------------------------------------------------|-----------|

| ⊂⊃ Process also test-wafer 2, <b>but not test-wafer 1</b> |          |                                                       |           |

| Temperature                                               | Duration | Flow rates                                            | Pressure  |

| ⊂⊃ 420°C                                                  | 20 min   | T° Stabilization + purge                              |           |

| ⊂⊃ 420°C                                                  | 15 min   | $SiH_4 = 30 \text{ cc/min} - O_2 = 60 \text{ cc/min}$ | 200 mTorr |

| ⊂⊃ 420°C                                                  | 10 min   | $N_2 = 1$ l/min (purge/vacuum)                        | 1 Torr    |

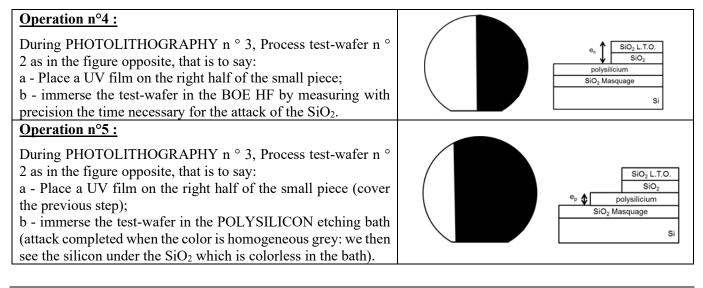

$\square$  Depth measurement of diffused junction on test-wafer 1 - **Operation n°3 (§ XIX)**  $\square$  Thickness measurement {oxide diffusion  $e_d + LTO$  oxide  $e_n$ } on test-wafer 2 using profilemeter - **Operation n°4 (§ XIX)**

$\bigcirc$  Deduce LTO oxide  $e_n$  thickness

# XII- PHOTOLITHOGRAPHY n° 3 : "CONTACTS OPENING"

|                                                 | Supervisor's visa for the continuation of Operations | ▼ |

|-------------------------------------------------|------------------------------------------------------|---|

| Operations                                      | Conditions                                           |   |

| $\bigcirc$ 1°) Drying                           | Hot plate 120°C – 2 min                              |   |

| ⊂⊃ 2°) HMDS deposit<br>(Adhesion promoter)      | Spin coater 4000 rpm - 30 s                          |   |

| $\subset 3^{\circ}$ ) Deposit resist            | Resist Shipley S1813<br>Spin coater 4000 rpm - 30 s  |   |

| $\subset \supset 4^{\circ}$ ) 1st annealing     | Hot plate $100^{\circ}C - 60 s$                      |   |

| $\bigcirc$ 5°) Alignment - Insolation           | Mask $n^{\circ}3 - 5 s$                              |   |

| $ ightarrow 6^{\circ}$ ) Development            | Bath à 20 °C - 35 s                                  |   |

| $ ightarrow 7^{\circ}$ ) Rinsing                | DI water                                             |   |

|                                                 | Spin dryer                                           |   |

| $\bigcirc$ 9°) Observation                      | Optical microscope                                   |   |

| $ ightarrow 10^{\circ}$ ) 2nd annealing         | Hot plate 120° C - 45 s                              |   |

| $\subset 11^{\circ}$ ) SiO <sub>2</sub> etching | BOE HF : time duration given by test-wafer2          |   |

| $\bigcirc$ 12°) Rinsing                         | DI water                                             |   |

| $\bigcirc$ 13°) Drying                          | Spin dryer                                           |   |

| $\subset 14^{\circ}$ ) Observation              | Optical microscope                                   |   |

| $ ightarrow 15^{\circ}$ ) Resist dissolution                                               | Acetone    |  |

|--------------------------------------------------------------------------------------------|------------|--|

| $\subset \supset 16^{\circ}$ ) Rinsing                                                     | DI water   |  |

| $ ightarrow 17^{\circ}$ ) Drying                                                           | Spin dryer |  |

| $\bigcirc$ 18°) Bring the components wafer to AIME staff for mounting on the sample holder |            |  |

⊃ POLYSILICON thickness measurement on test-wafer 2 - Operation n°5 (§ XIX)

# **XIII- METALLIZATION**

A 300 nm thick Aluminium layer is deposited on the wafer in this step.

| Either by RF magnetron sputtering | ⊂⊃ Deposit | Pressure before Deposit =<br>Pressure during Deposit =<br>Power RF = | 10 <sup>-7</sup> mbar<br>2.10 <sup>-3</sup> mbar<br>150 W |

|-----------------------------------|------------|----------------------------------------------------------------------|-----------------------------------------------------------|

|                                   |            | Target-substrate distance =<br>Duration of the Deposit =             | 90 mm<br>15 min                                           |

<u>OR</u>

by thermal evaporation

| ⊂⊃ Degassing | T(subst.) =<br>Duration =                              | °C<br>min    |

|--------------|--------------------------------------------------------|--------------|

| ⊂⊃ Deposit   | Pressure before Deposit =<br>Pressure during Deposit = | mbar<br>mbar |

#### PHOTOLITHOGRAPHY n° 4 : "METAL ETCHING" XIV-

| Supervisor's visa for the continuation of Operations         |                                                                  |  |

|--------------------------------------------------------------|------------------------------------------------------------------|--|

| Operations                                                   | Conditions                                                       |  |

| $\bigcirc 0^{\circ}$ ) Aluminum etching bath homogenization. | Switch on the ultrasonic cleaner containing the Al etching bath. |  |

| $\subset 1^{\circ}$ ) Drying                  | Hot plate 120°C – 2 min                                                                                                                                                                      |   |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| $\bigcirc 2^{\circ}$ ) Resist deposit         | Resist Shipley S1813<br>Spin coater 4000 rpm - 30 s                                                                                                                                          |   |

| Si                                            | upervisor's visa for the continuation of Operations                                                                                                                                          | ▼ |

| $\bigcirc$ 3°) 1st annealing                  | Hot plate $100^{\circ}C - 60 s$                                                                                                                                                              |   |

| $\bigcirc 4^{\circ}$ ) Alignment - Insolation | Mask $n^{\circ}4 - 5$ s                                                                                                                                                                      |   |

| $\bigcirc 5^{\circ}$ ) Development            | Bath à 20 °C - 25 s                                                                                                                                                                          |   |

| $\subset 5^{\circ}$ ) Rinsing                 | DI water                                                                                                                                                                                     |   |

| $\bigcirc$ 7°) Drying                         | Spin dryer                                                                                                                                                                                   |   |

| $ ightarrow 8^{\circ}$ ) Observation          | Optical microscope                                                                                                                                                                           |   |

| $\bigcirc 9^{\circ}$ ) 2nd annealing          | Hot plate 120° C - 45 s                                                                                                                                                                      |   |

| $ ightarrow 10^\circ$ ) Bath of Al etching    | Stop the ultrasonic cleaner, and take out the Al etching bath                                                                                                                                |   |

| ⊂⊃ 11°) Al ETCHING                            | Al etching bath<br>(40vol. H <sub>3</sub> PO <sub>4</sub> + 7vol. HNO <sub>3</sub> + 7vol. H <sub>2</sub> O)<br>using <b>final control with naked eye</b><br>+ 30 s of supplementary etching |   |

| $\subset \supset 12^{\circ}$ ) Rinsing        | DI water                                                                                                                                                                                     |   |

| ightarrow 13°) Drying                         | Spin dryer                                                                                                                                                                                   |   |

| $\subset 14^{\circ}$ ) Observation            | Optical microscope                                                                                                                                                                           |   |

This photolithography is followed by the oxide etching of the backside of the components wafer.

| Supervisor's visa for the continuation of Operations |                                                                                                                                                                                      |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\bigcirc$ 15°) Front side protection                | UV film                                                                                                                                                                              |  |

| ⊂⊃ 16°) POLYSILICON ETCHING<br>backside              | POLYSILICON etching bath<br>(1vol. <b>HF</b> + 71vol.HNO <sub>3</sub> + 28vol.H <sub>2</sub> O)<br>using <b>final control with naked eye</b><br>: homogeneous grey color in the bath |  |

| $\subset 17^{\circ}$ ) De-oxidation backside         | BOE HF (attaque SiO <sub>2</sub> grille)<br>using <b>final control with naked eye</b><br>checking the hydrophobicity of the backside                                                 |  |

| $\bigcirc$ 18°) Rinsing                              | DI water                                                                                                                                                                             |  |

| $\bigcirc$ 19°) Drying                               | Spin dryer                                                                                                                                                                           |  |

| $\bigcirc 20^{\circ}$ ) UV film glue degradation     | UV Light– 5 min                                                                                                                                                                      |  |

| $\bigcirc$ 21°) Cleaning resist (2 faces)            | Acetone                                                                                                                                                                              |  |

| $\bigcirc$ 22°) Rinsing | DI water   |

|-------------------------|------------|

| $\bigcirc$ 23°) Drying  | Spin dryer |

#### XV- METAL ANNEALING

This Operation is carried out in oven n ° 3-2 according to the conditions:

| Temperature | Duration | Flow rates                |

|-------------|----------|---------------------------|

| ⊂⊃ 400°C    | 20 min   | $N_2 + H_2$ (5%)= 1 l/min |

⊂⊃ Aluminum thickness measurement on "components" wafer using the profilemeter

$\subset$  Fill in the 1st part of the results sheet before the wafer probing test

## XVI- WAFER PROBING

$\bigcirc$  Quickly map the wafer to determine the region where the best components are located and select them.

#### XVII- ASSEMBLY

$\Box$  DICING of the "components" wafer with a diamond blade

$\bigcirc$  MOUNTING on base: welding by gold-silicon eutectic at T = 370 ° C

$\square$  MICRO-WELDING by ultrasound (wedge bonding of Al-Si wire 5%,  $\emptyset$  25µm)

#### **XVIII-ELECTRICAL TEST**

See "characterization" pages

#### 1°) - Measurement I(V) :

$\subset$  Trace the I<sub>D</sub> (V<sub>DS</sub>) characteristics of a long channel transistor

$\subset$  Trace the I<sub>D</sub> (V<sub>GS</sub>) characteristics of a long channel transistor

$\square$  Trace the I<sub>D</sub> (V<sub>DS</sub>) characteristics of a short channel transistor

$\Box$  Trace the I<sub>D</sub> (V<sub>GS</sub>) characteristics of a short channel transistor

$\subset$  Plot the characteristic I (V) of the diode

#### 2°) - Measurement C(V) :

$\subset \supset$  Plot the characteristic C = f (V) of the MOS capacitance

# XIX- OPERATIONS ON THE TEST WAFER

#### **TEST** WAFER 1:

#### TEST WAFER 2 :

# XX- CHARACTERIZATIONS

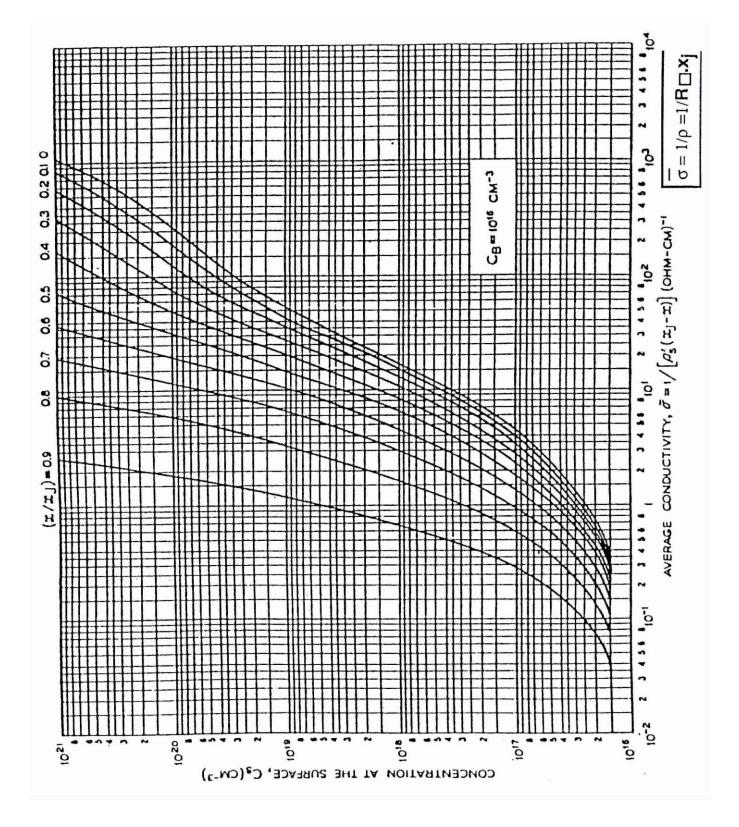

#### I- SUBSTRATE CHARACTERIZATION:

| At the start of the process, we measure:      | We deduce:                     |                    |

|-----------------------------------------------|--------------------------------|--------------------|

| - the four points measurement : $V/I = $ Ω    | $\rightarrow R_{as} =$         | Ω                  |

|                                               |                                |                    |

| - the thickness of the slices: $e_s = \\mu m$ | $\rightarrow \rho_s =$         | <u>Ω</u> .cm       |

|                                               |                                |                    |

|                                               | $\rightarrow$ N <sub>A</sub> = | at/cm <sup>3</sup> |

|                                               |                                |                    |

#### **II - MEASUREMENTS OF OXIDE THICKNESSES:**

| a- Masking oxide after Operation II  | $e_m = \ \mu m$  |

|--------------------------------------|------------------|

| b- Gate oxide after Operation VI     | $e_g = \ \mu m$  |

| c- Diffusion oxide after Operation X | $e_d = \{\mu m}$ |

| d- L.T.O. after Operation XI $e_n =$ | <u></u> μm       |

#### **III-** CHARACTERIZATION OF THE DIFFUSION:

After step X (diffusion of the substrate), Measurements of :

| V/I =            | Ω  | $\rightarrow$ | $R_{nd} = $      | Ω       |

|------------------|----|---------------|------------------|---------|

| X <sub>j</sub> = | μm | $\rightarrow$ | $\rho_d =$       | Ω.cm    |

|                  |    | $\rightarrow$ | C <sub>s</sub> = | at /cm3 |

#### **IV-** CHARACTERIZATION OF THE DOPED POLYSILICON LAYER:

After step X (diffusion of the substrate), Measures of :

| V/I =            | Ω   | $\rightarrow$ | R <sub>p</sub> = | Ω     |

|------------------|-----|---------------|------------------|-------|

| e <sub>p</sub> = | _μm | $\rightarrow$ | $\rho_p =$       | _Ω.cm |

#### V-ELECTRICAL TESTS:

The list of measurements mentioned below is given by way of example to allow either comparisons with theoretical values or the determination of new technological parameters.

1 - For each of the transistors of a chip:

$\Box$  Trace the network of characteristics  $I_D$  (V<sub>DS</sub>) and  $I_D$  (V<sub>GS</sub>) and deduce

- • g<sub>m</sub> transconductance

- • the on-state resistance  $R_{on}$  (for  $V_{GS} = 5 \text{ V}$ )<sup>1</sup>

$\bigcirc$  We can also evaluate:

- Current  $I_{DS0}$  at  $V_{GS}=0$

- the threshold voltage V<sub>T</sub>

- the breakdown voltage V<sub>B</sub>

To be able to do the calculations, it is necessary to know the geometric dimensions of the components produced:

Transistor MOS "long channel"

$L = \__{\mu m} - W = \__{\mu m}$

$g_m = \dots mS$   $R_{on} = \dots \Omega$

$V_T = V \quad V_B = V \quad I_{DS0} = \mu A$

| Transistor MOS "short channel"           |  |  |    |

|------------------------------------------|--|--|----|

| L = µm - $W = $ µm                       |  |  |    |

| $g_m = \dots mS$ $R_{on} = \dots \Omega$ |  |  | 2  |

| $V_T = V  V_B = V  I_{DS0} = \mu $       |  |  | μA |

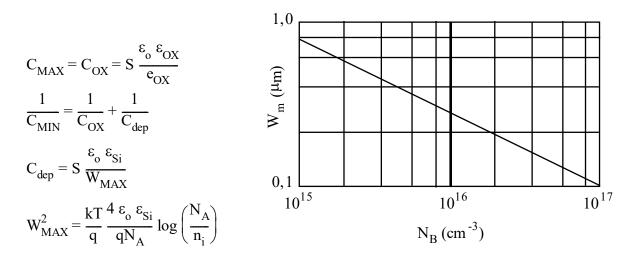

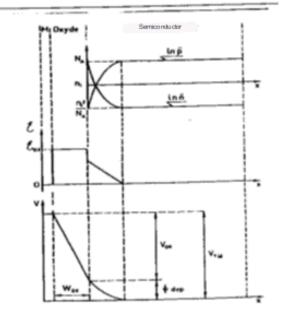

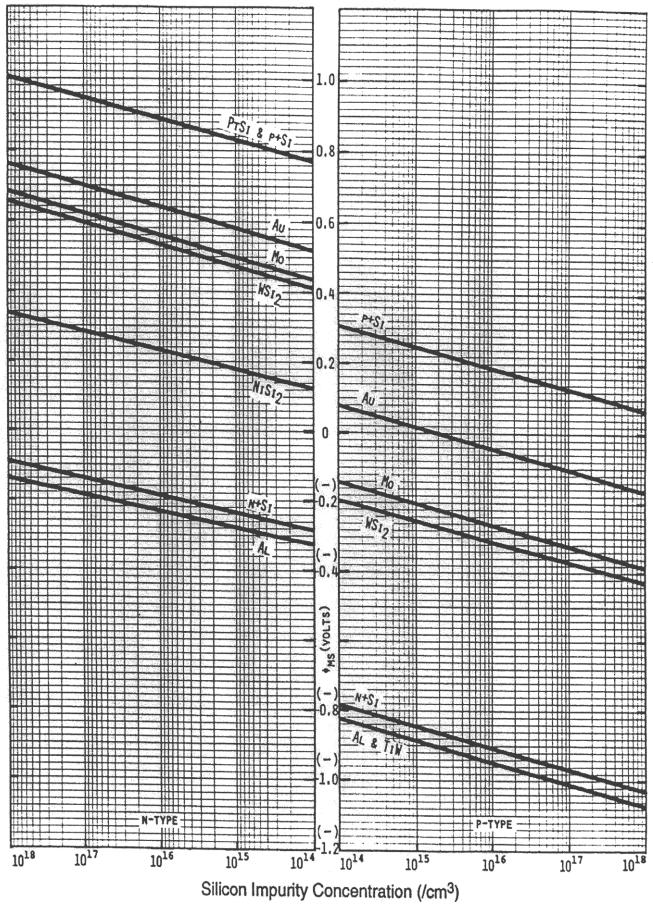

<u>2 – For the MOS capacitor:</u>

$\subset \supset$  Draw the curve C (V) in high frequencies and deduce from it C<sub>ox</sub>, C<sub>dep</sub>, V<sub>T</sub> et Q<sub>SS</sub> :

| MOS Capacitor :   | $S = cm^2$                 |

|-------------------|----------------------------|

| $C_{ox} = \pF$    | $e_{ox} = \dots \mu m$     |

| $C_{dep} = \pF$   |                            |

| V <sub>T</sub> =V | $N_{ox} = charges.cm^{-2}$ |

<sup>&</sup>lt;sup>1</sup> The experimental value  $R_{on}$  is obtained by measuring the slope of the characteristic  $I_D(V_{DS})$ à  $V_{GS}$  = constant in the region where the current increases linearly with the voltage.

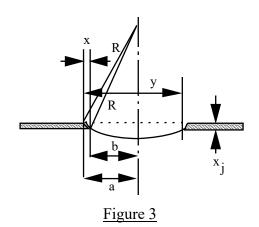

# XXI-MEASUREMENT OF JUNCTION DEPTHS

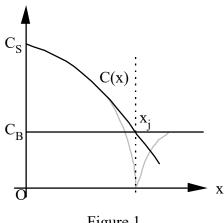

#### **DEFINITION:**

Xj is the distance counted from the silicon surface such that  $C(Xj) = C_B$

C (x) corresponding to the doping profile of the diffused zone and  $C_B$  to that of the substrate.

#### **PROCEDURE:**

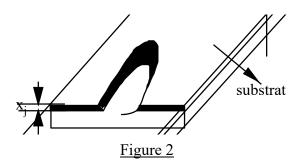

a- Mechanical digging of the sample by a cylinder of radius R coated with diamond paste to obtain an imprint with a depth greater than Xj.

b- Chemical revelation which colors the N zone and the P zone differently.

c- Observation under Optical microscope and measurement of quantities x and y (fig. 3).

#### **CALCULATION OF XJ:**

With the notations in the figure, the measured lengths x and y are such that:

$$\begin{array}{l} x=a -b \\ y=a+b \end{array} \right\} \quad xy=a^2 -b^2 \\ \end{array}$$

In addition, simple geometric considerations lead to:

$$x_{j} = \{R^{2} - b^{2}\}^{\frac{1}{2}} - \{R^{2} - a^{2}\}^{\frac{1}{2}}$$

$$8 R \left\{ \left(1 - \frac{b^{2}}{2R^{2}}\right) - \left(1 - \frac{a^{2}}{2R^{2}}\right) \right\} = \frac{xy}{2R}$$

$$= \frac{xy}{2R}$$

Taking into account the radius of the cylinder R = 1.25 cm and the magnification of the microscope, we have:

**objective X 3,2** 1 division of Vernier screw  $\rightarrow 1 \ \mu m$  and

$$x_{j} (\mu m) = 39.9 . 10^{-6} x_{(div)} . y_{(div)}$$

**objective X 5** 1 division of Vernier screw  $\rightarrow 0,6$  µm and

$$x_{j} (\mu m) = 14,40 . 10^{-6} x_{(div)} . y_{(div)}$$

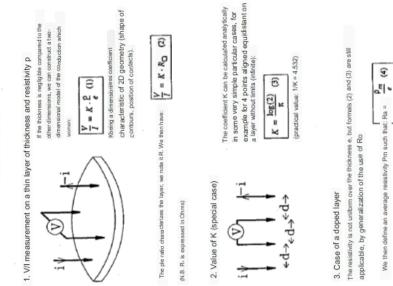

Resistance of a conductive track of length whoed): Let and width W (a parallel

where Let W characterizes the design of the  $R = \rho \cdot \frac{L}{S} = \rho \cdot \frac{L}{eW} = \frac{L}{W} \cdot R_{\mathbf{Q}}$

ନ

masks while R characterizes the

technology. The L/N ratio can be considered as a "number of squares", hence the name Ro: ssistance per square".

# 5. Case of significant thickness

If the thickness of the layer is not negligible but still reasonably small, formulas (2) and (3) can be applied by replacing K by a corrected K coefficient, a function of the ratio between the thickness and the other dimensions.

In the case of the 4 equidistant points of distance d, the correction is negligible as long as:

- perform a V/I measurement not too close to the edges of the sample Practical method for measuring 4 points:

- int in Ohms express the .

- multiply by 4.532 to obtain R, note this result (always in Ohms) .

- correction is not (the distance between points being 1.59 mm, the thick express the thickness of the layer in cm.

- multiply Ropar e to obtain the resistivity for Pm note this result (in

- Ohm.cm) use an abacus to deduce the dopant concentration (after possibly calculation of conductivity in Chim<sup>1</sup>.cm<sup>21</sup>). .

- SiBL ATTENTION: it is not the same chart depending on whether the dop deposited polysilicon) or not (diffused or implanted layer).

ation can be deduced at the surface

If the dopant distribution law is known, Pla concent and for different depths (see charts).

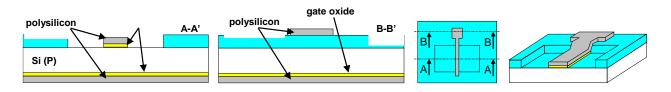

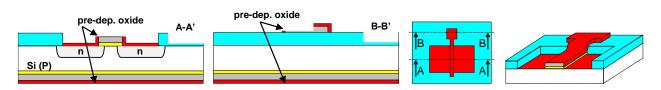

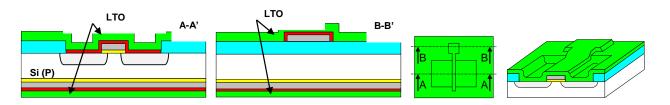

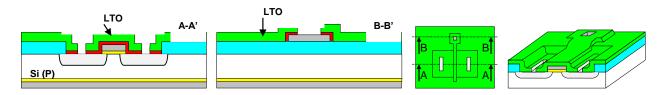

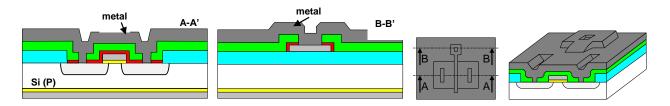

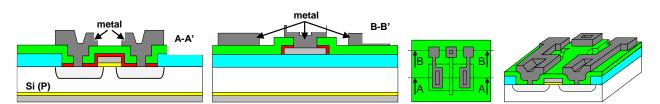

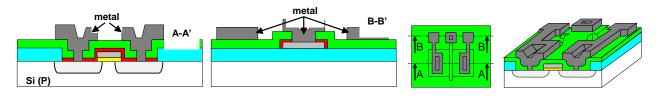

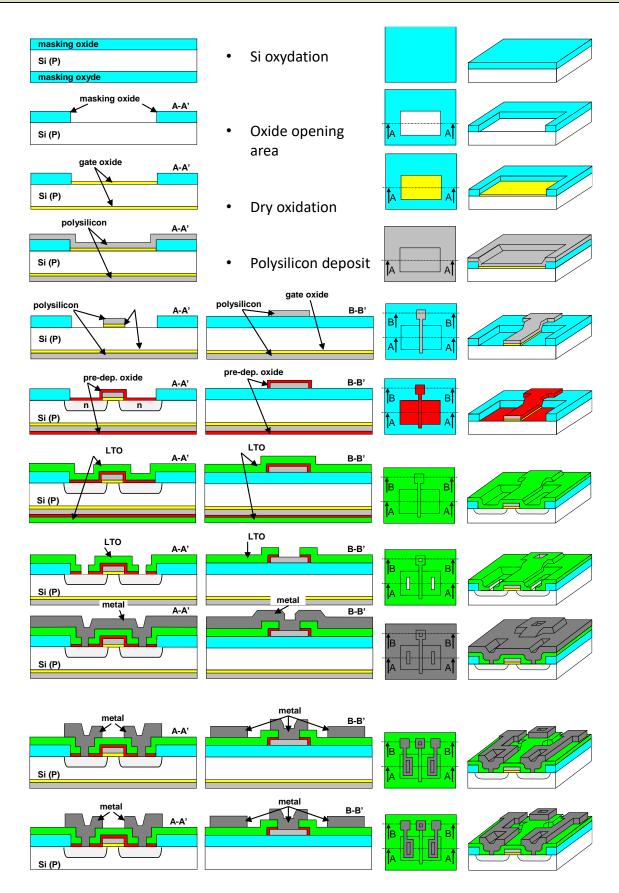

#### XXIII-SECTIONAL VIEWS OF THE DIFFERENT STAGES OF THE PROCESS

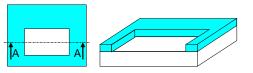

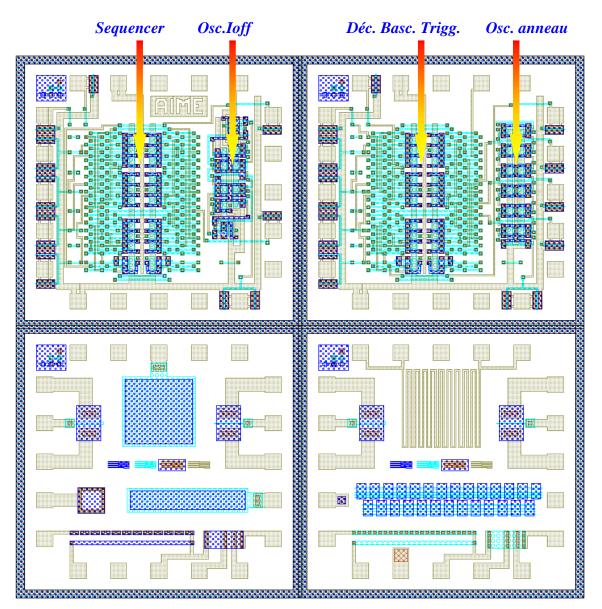

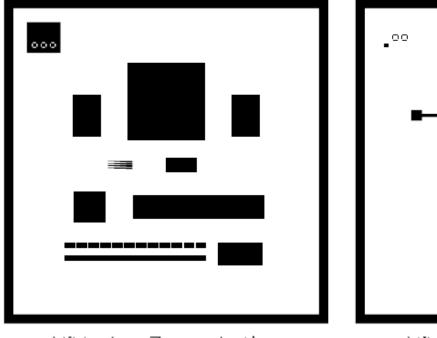

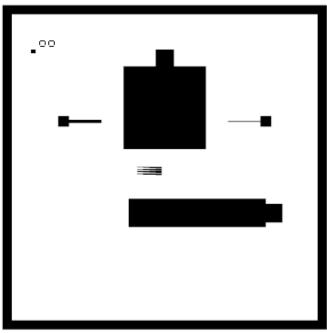

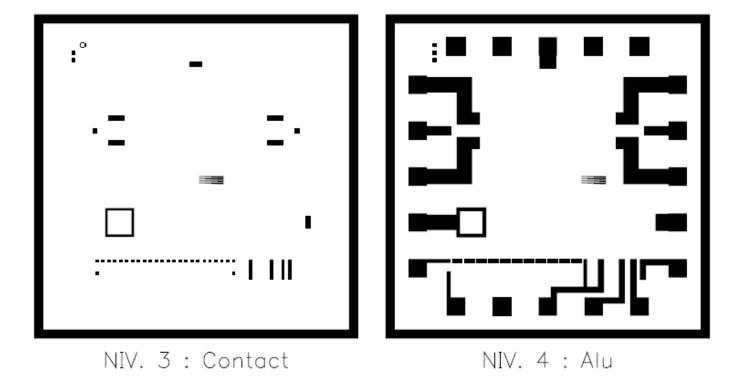

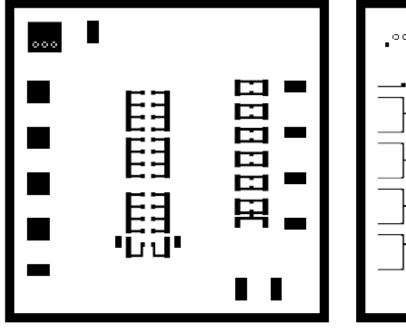

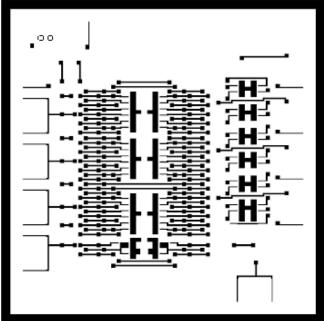

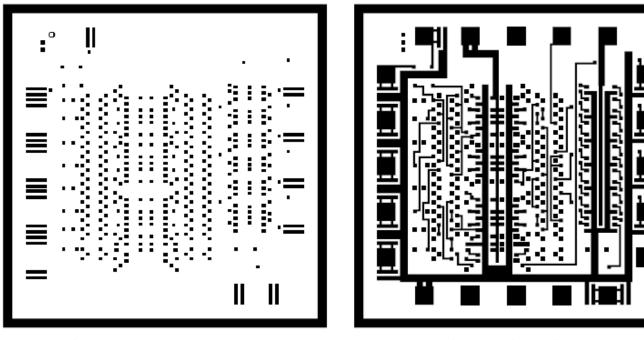

# XXIV-SET OF MASKS DTC4R

# **CHIP C3**

# **CHIP C4**

# **CHIP C1**

**CHIP C2**

# DTC4R : CHIP C1

NIV. 1 : Zone Active

NIV. 2 : Polysilicum

# DTC4R : CHIP C4

NIV. 1 : Zone Active

NIV. 2 : Polysilicum

NIV. 3 : Contact

#### XXV- FORMS FOR ELECTRICAL TESTS

#### I- MOS CAPACITOR (Substrate P, High frequency Measurement (1 MHz))

# II- TRANSCONDUCTANCE OF A MOS TRANSISTOR (saturated regime) $Z = \frac{\varepsilon_0 \varepsilon_{OX}}{\varepsilon_0 \varepsilon_{OX}} = \frac{\varepsilon_0 \varepsilon_{OX}}{\varepsilon_0 \varepsilon_{OX}}$

$$g_{\rm m} = \frac{Z}{L} \mu_{\rm n} \frac{e_{\rm o} e_{\rm OX}}{e_{\rm OX}} (V_{\rm G} - V_{\rm T}) \longrightarrow Z \frac{e_{\rm o} e_{\rm OX}}{e_{\rm OX}} v_{\rm s}$$

# III- THRESHOLD VOLTAGE (channel N)

$$V_{T mes} = V_{T id} - \frac{Q_{SS}}{C_{OX}} \text{ ou } N_{SS} = (V_{T mes} - V_{T id}) \frac{C_{OX}}{q S} (cm^{-2})$$

et  $V_{T id} = \Phi_{ms} + 2 \Phi_{F} + \sqrt{2 \Phi_{B} \Phi_{F}}$

avec  $\Phi_{B} = 2 N_{A} \frac{e_{OX}^{2}}{\varepsilon_{o} \varepsilon_{OX}} \frac{\varepsilon_{Si}}{\varepsilon_{OX}} \Phi_{F} = \frac{kT}{q} \log \frac{N_{A}}{n_{i}}$

$\Phi_{ms} = \Phi_{m} - \left(X_{si} + \frac{Eg}{2q} + \Phi_{F}\right)$

#### IV- SOME NUMERICAL VALUES (Si, T = 300 °K)

$$U_{T} = \frac{kT}{q} = 0,0259 \text{ V} \quad ; \quad \frac{E_{g}}{2q} = 0,56 \text{ V} \quad ; \quad n_{i} = 1,45 \cdot 10^{10} \text{ cm}^{-3}$$

$$\varepsilon_{Si} = 11,9 \quad ; \quad \varepsilon_{OX} = 3,9 \quad ; \quad \varepsilon_{o} = 8,85 \cdot 10^{-14} \text{ F.cm}^{-1} \quad ; \quad v_{s} = 10^{7} \text{ cm.s}^{-1}$$

Pour une grille en Al :  $\Phi_{m} - x_{Si} = -0,11 \text{ V}$

#### V- SILICON DOPING

Version 2021

Theoretical calculation of the threshold voltage V, of the MOS

#### Notations

- Wo and Wsi work on grid output and the S, respectively.

- $\phi_{m} = \frac{Wo-Ws}{q}$  equivalent voltage of the output work difference

- dep: tension supported by the depopulated zone of thickness Wdep max

- AVox: voltage supported by the gate oxide at threshold.

- Qss: charge in C/cm<sup>2</sup> in the oxide (negative charge in the channel)

- Nss = Q<sub>ss</sub> equivalent in atoms/cm<sup>2</sup> q

- eox- gate oxide thickness

- Cox = Eox/eox

Capacity of gate oxide per unit area

□ threshold voltage V,VT + V must be >0 in the NMOS

VFB: negative flat band voltage

$$V_{PB} = \frac{W_{c} - W_{s_{i}}}{q} - \frac{Q_{ss}}{C_{ox}} < 0$$

Ideal case

m0 and Qss-0

VTid AVox+dp>0 in NMOS Pop-2UT In NA n

$$\Delta V_{ox} = \frac{e_{ox}}{\epsilon_{ox}} \sqrt{2q\epsilon_{si}N_{A}\varphi_{dep}}$$

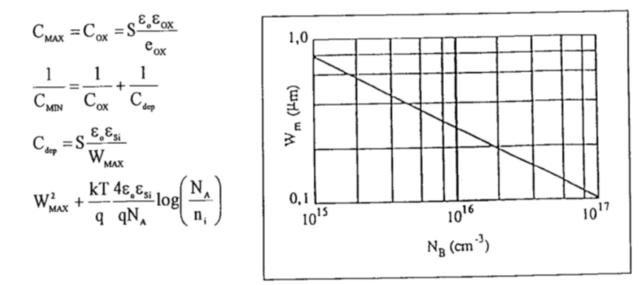

#### About $\phi_{ms}$

The following chart makes it possible to determine the difference in output work between ga and Si according to the type of substrate (N or P) and according to its doping and for variou of gates (Poly SN, Poly S.P' or Al).

Ex : substrat P. N₄=10<sup>16</sup>. Grille N<sup>+</sup>Si⇒oms≅-0,8V

Dielectric data

$\varepsilon_{OX}$ =3,9  $\varepsilon_{0}$  $\varepsilon_{0}$ =8,85.10<sup>-14</sup>F/cm  $\varepsilon_{Si}$ =11,9  $\varepsilon_{0}$

Data S, at 300°K: intrinsic density ni=1010 cm-3

band gap v

$$Eg=1,12eV$$

thermodynamic voltage  $U_{T}=\frac{kT}{q}=26mV$

#### 11

MOS capacity (Substrate P, High frequency measurements (1 MHZ))

III Transconductance of a MOS transistor (saturated mode)

$$g_{m} = \frac{Z}{L} \mu_{m} \frac{\varepsilon_{o} \varepsilon_{ox}}{e_{ox}} (V_{G} - V_{T}) \longrightarrow Z \frac{\varepsilon_{o} \varepsilon_{ox}}{e_{ox}} v_{s}$$

# ΦMS versus Silicon Doping for Various Gate Electrodes